# YW820 PRELIMINARY

# NSX-1

### Overview

YMW820 or NSX-1 is a sound generator device for consumer applications with wavetable synthesis core supporting up to 64 simultaneous voices. It already is a high-end ROM-based General MIDI- or GM-compliant sound module, and when waveforms are put on its large on-chip RAM it makes a wavetable synthesizer with the superb quality and expressiveness that can come close to real musical instruments.

It also integrates powerful RISC processor to control these sound generator cores, and it frees up the host controller from these chores.

The host controller may also load programs and wave samples on the on-chip RAM to extend NSX-1 with such features as VOCALOID--Yamaha's renowned singing synthesizer technology. And, the flexibility provided from having large set of power off- and power save-modes enables the device to be used in most products in today's portable device applications.

The information provided is preliminary, and subject to change without notice. Please check for the latest information when using this product in your design.

YAMAHA CORPORATION

YMW820 CATALOG CATALOG No. LSI-4MW820A00 2012.01

PRELIMINARY

Features

YMW820

#### Features

• YMW820 is the sound generator device for consumer applications

#### [Sound Generator]

- Wavetable synthesis core supporting up to 64 simultaneous voices

- · Sampling frequency: 44.1 kHz

- Large on-chip memories for waveforms

- ➤ 2 Mbyte RAM (for typical use)

The total 3 Mbyte of on-chip RAM can be partitioned into waveform storage (up to

- 2 Mbyte) and secondary work area for integrated CPU.

- > GM (General MIDI) sound presets ROM

- · Integrated DSP for audio effect processing

- · 2 digital audio inputs

- Supports I<sup>2</sup>S / Left-justified / Right-justified / PCM format

- > Sampling frequency: 8 kHz to 48 kHz

- > Supports both Master mode and Slave mode

- · 2 digital audio outputs

- Supports I<sup>2</sup>S / Left-justified / Right-justified / PCM format

- > Sampling frequency: 8 kHz to 48 kHz

- > Supports both Master mode and Slave mode

#### [Integrated CPU]

- Powerful dual-issue 32-bit RISC processor

- Two selectable clock rates (135.4752 MHz or 67.7376 MHz)

- Caches (8 Kbyte for Instruction, 8 Kbyte for Data)

- Large integrated work memories

- · Primary work area

- No wait accesses from the processor

- · Secondary work area (1 Mbyte for typical use)

The total 3 Mbyte of on-chip RAM can be partitioned into secondary work area (up to 3 Mbyte) and waveform storage.

- Integrated peripherals: DMAC, timer/counters, watchdog timer, and IRQ controller

- 3 programmable GPIO pins

PRELIMINARY

■ Features YMW820

- Sound Inputs and Outputs

- · Integrated CPU accepts and processes sounds from the host controller, Sound Generator, and the one on the digital audio interface

- · Integrated CPU outputs and Sound Generator outputs can be mixed

- Host Controller Interface

- · Parallel 8- or 16-bit bus

- · SPI. Supports 4 communication formats

- Mode 0: Positive pulse clocks; data sampled on rises, toggled on falls

- Mode 1: Positive pulse clocks; data toggled on rises, sampled on falls

- Mode 2: Negative pulse clocks; data sampled on falls, toggled on rises

- Mode 3: Negative pulse clocks; data toggled on falls, sampled on rises

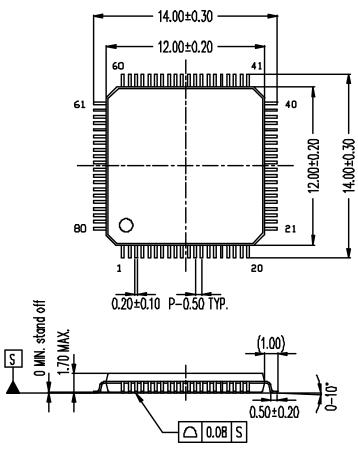

#### [Package]

- Lead-free 80-pin SQFP package (YMW820-SZ)

- 12 mm×12 mm

- Pin pitch 0.5 mm

#### [Power Supply]

• Core supply (DVDD) :1.02 V to 1.20 V (1.10 V typical)

• I/O supply (IOVDD\*) :1.65 V to 3.60 V

#### [Others]

Power off- and Power save-modes

Power consumption can be minimized with the large set of power off- and power save-modes

PRELIMINARY

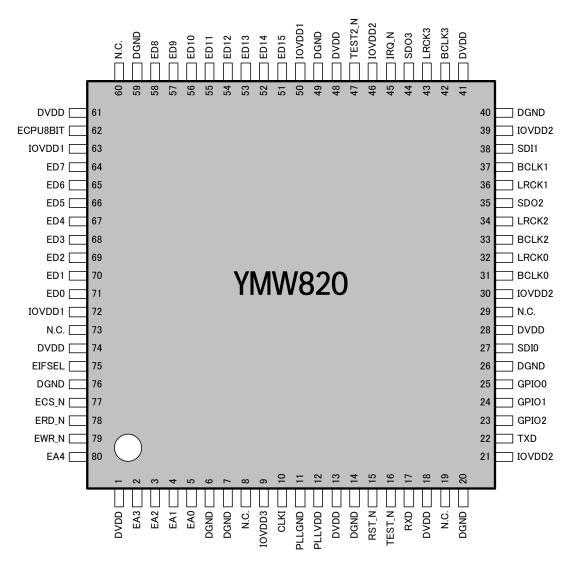

Pin Assignments

YMW820

# **■** Pin Assignments

# < Top View >

<80pin SQFP Top View>

PRELIMINARY

■ Pin Descriptions

YMW820

# **■** Pin Descriptions

| No. | Pin name          | I/O       | Power supply | Description                                                                               |

|-----|-------------------|-----------|--------------|-------------------------------------------------------------------------------------------|

| 1   | DVDD              | P         |              | Digital core supply (1.1 V)                                                               |

| 2   | EA3<br>/ SPI_MODE | I         | IOVDD1       | (EIFSEL="L") Host controller parallel interface Address 3 (EIFSEL="H") SPI mode           |

| 3   | EA2<br>/ ESI      | I         | IOVDD1       | (EIFSEL="L") Host controller parallel interface Address 2 (EIFSEL="H") SPI data input     |

| 4   | EA1<br>/ ESCK     | I         | IOVDD1       | (EIFSEL="L")Host controller parallel interface Address 1<br>(EIFSEL="H") SPI clock input  |

| 5   | EA0<br>/ ESS_N    | I         | IOVDD1       | (EIFSEL="L") Host controller parallel interface Address 0<br>(EIFSEL="H") SPI chip select |

| 6   | DGND              | G         | _            | Digital core ground                                                                       |

| 7   | DGND              | G         | _            | Digital core ground                                                                       |

| 8   | N.C.              | N.C.      |              |                                                                                           |

| 9   | IOVDD3            | P         |              | IO supply (1.65 V to 3.60 V)                                                              |

| 10  | CLKI              | Ish/Itcxo | IOVDD3       | Clock input (10 MHz to 27 MHz)                                                            |

| 11  | PLLGND            | G         | _            | PLL ground                                                                                |

| 12  | PLLVDD            | P         | _            | PLL supply (1.1V)                                                                         |

| 13  | DVDD              | P         | _            | Digital core supply (1.1 V)                                                               |

| 14  | DGND              | G         | _            | Digital core and IO ground                                                                |

| 15  | RST_N             | Ish       | IOVDD2       | Hardware reset input                                                                      |

| 16  | TEST_N            | Ish       | IOVDD2       | Test pin                                                                                  |

| 17  | RXD               | Ish       | IOVDD2       | Receive data input                                                                        |

| 18  | DVDD              | P         | _            | Digital core supply (1.1 V)                                                               |

| 19  | N.C.              | N.C.      | _            |                                                                                           |

| 20  | DGND              | G         | _            | Digital core and IO ground                                                                |

| No. | Pin name | I/O  | Power supply | Function                              |             |  |  |

|-----|----------|------|--------------|---------------------------------------|-------------|--|--|

| 21  | IOVDD2   | P    |              | IO supply (1.65 V to 3.60 V)          |             |  |  |

| 22  | TXD      | О    | IOVDD2       | Transmit data output                  |             |  |  |

| 23  | GPIO2    | I/O  | IOVDD2       | GPIO                                  |             |  |  |

| 24  | GPIO1    | I/O  | IOVDD2       | GPIO                                  |             |  |  |

| 25  | GPIO0    | I/O  | IOVDD2       | GPIO                                  |             |  |  |

| 26  | DGND     | G    | _            | Digital core and IO ground            |             |  |  |

| 27  | SDI0     | I    | IOVDD2       | Digital audio interface #0 input data |             |  |  |

| 28  | DVDD     | P    | _            | Digital core supply (1.1 V)           |             |  |  |

| 29  | N.C.     | N.C. |              |                                       |             |  |  |

| 30  | IOVDD2   | P    |              | IO supply (1.65 V to 3.60 V)          |             |  |  |

| 31  | BCLK0    | I/O  | IOVDD2       | Digital audio interface#0             | Bit clock   |  |  |

| 32  | LRCK0    | I/O  | IOVDD2       | Digital audio interface#0             | LR clock    |  |  |

| 33  | BCLK2    | I/O  | IOVDD2       | Digital audio interface#2             | Bit clock   |  |  |

| 34  | LRCK2    | I/O  | IOVDD2       | Digital audio interface#2             | LR clock    |  |  |

| 35  | SDO2     | О    | IOVDD2       | Digital audio interface#2             | Output data |  |  |

| 36  | LRCK1    | I/O  | IOVDD2       | Digital audio interface#1             | LR clock    |  |  |

| 37  | BCLK1    | I/O  | IOVDD2       | Digital audio interface#1             | Bit clock   |  |  |

| 38  | SDI1     | I    | IOVDD2       | Digital audio interface#1             | Input data  |  |  |

| 39  | IOVDD2   | P    | _            | IO supply (1.65 V to 3.60 V)          |             |  |  |

| 40  | DGND     | G    | _            | Digital core and IO ground            |             |  |  |

| No. | Pin name | I/O  | Power supply | Function                           |             |  |  |

|-----|----------|------|--------------|------------------------------------|-------------|--|--|

| 41  | DVDD     | P    | _            | Digital core supply (1.1 V)        |             |  |  |

| 42  | BCLK3    | I/O  | IOVDD2       | Digital audio interface#3          | Bit clock   |  |  |

| 43  | LRCK3    | I/O  | IOVDD2       | Digital audio interface#3          | LR clock    |  |  |

| 44  | SDO3     | О    | IOVDD2       | Digital audio interface#3          | Output data |  |  |

| 45  | IRQ_N    | О    | IOVDD2       | Interrupt request                  |             |  |  |

| 46  | IOVDD2   | P    | _            | IO supply (1.65 V to 3.60 V)       |             |  |  |

| 47  | TEST2_N  | Ish  | IOVDD2       | Test pin. Always tied to DGND.     |             |  |  |

| 48  | DVDD     | P    | _            | Digital core supply (1.1 V)        |             |  |  |

| 49  | DGND     | G    | _            | Digital core and IO ground         |             |  |  |

| 50  | IOVDD1   | P    | _            | IO supply (1.65 V to 3.60 V)       |             |  |  |

| 51  | ED15     | I/O  | IOVDD1       | Host controller parallel interface | Data 15     |  |  |

| 52  | ED14     | I/O  | IOVDD1       | Host controller parallel interface | Data 14     |  |  |

| 53  | ED13     | I/O  | IOVDD1       | Host controller parallel interface | Data 13     |  |  |

| 54  | ED12     | I/O  | IOVDD1       | Host controller parallel interface | Data 12     |  |  |

| 55  | ED11     | I/O  | IOVDD1       | Host controller parallel interface | Data 11     |  |  |

| 56  | ED10     | I/O  | IOVDD1       | Host controller parallel interface | Data 10     |  |  |

| 57  | ED9      | I/O  | IOVDD1       | Host controller parallel interface | Data 9      |  |  |

| 58  | ED8      | I/O  | IOVDD1       | Host controller parallel interface | Data 8      |  |  |

| 59  | DGND     | G    | _            | Digital core and IO ground         |             |  |  |

| 60  | N.C.     | N.C. | _            |                                    |             |  |  |

| No. | Pin name | I/O  | Power supply | Function                                                  |

|-----|----------|------|--------------|-----------------------------------------------------------|

| 61  | DVDD     | P    | _            | Digital core supply (1.1 V)                               |

| 62  | ECPU8BIT | I    | IOVDD1       | Host controller parallel interface Bus width select       |

| 63  | IOVDD1   | P    | _            | IO supply (1.65 V to 3.60 V)                              |

| 64  | ED7      | I/O  | IOVDD1       | Host controller parallel interface Data 7                 |

| 65  | ED6      | I/O  | IOVDD1       | Host controller parallel interface Data 6                 |

| 66  | ED5      | I/O  | IOVDD1       | Host controller parallel interface Data 5                 |

| 67  | ED4      | I/O  | IOVDD1       | Host controller parallel interface Data 4                 |

| 68  | ED3      | I/O  | IOVDD1       | Host controller parallel interface Data 3                 |

| 69  | ED2      | I/O  | IOVDD1       | Host controller parallel interface Data 2                 |

| 70  | ED1      | I/O  | IOVDD1       | Host controller parallel interface Data 1                 |

| 71  | ED0      | I/O  | IOVDD1       | Host controller parallel interface Data 0                 |

| 72  | IOVDD1   | P    | _            | IO supply (1.65 V to 3.60 V)                              |

| 73  | N.C.     | N.C. | _            |                                                           |

| 74  | DVDD     | P    | _            | Digital core supply (1.1 V)                               |

| 75  | EIFSEL   | I    | IOVDD1       | Host controller: parallel interface / SPI select          |

| 76  | DGND     | G    | _            | Digital core and IO ground                                |

| 77  | ECS_N    | I    | IOVDD1       | Host controller parallel interface Chip select            |

| 78  | ERD_N    | I    | IOVDD1       | Host controller parallel interface Read                   |

| 79  | EWR_N    | I/O  | IOVDD1       | (EIFSEL="L") Host controller parallel interface Write     |

| 19  | / ESO    | 1/0  | וטעטטו       | (EIFSEL="H") SPI Data Output                              |

| 90  | EA4      | т    | IOVDD1       | (EIFSEL="L") Host controller parallel interface Address 4 |

| 80  | / HOLD_N | I    | IOVDD1       | (EIFSEL="H")SPI Hold                                      |

| Symbols |                                                  |

|---------|--------------------------------------------------|

| I       | Digital input                                    |

| О       | Digital output                                   |

| I/O     | Digital input and output                         |

| Ish     | Digital input (Schmitt trigger input)            |

| Itcxo   | Digital input(TCXO)                              |

| P       | Power supplies                                   |

| G       | GND                                              |

| N.C.    | No Connect (pin is not connected anywhere in the |

| N.C.    | device)                                          |

#### N.C.: No Connect

No problem occurs even if connected to a supply voltage line, a ground line, or a signal line on a board. In addition, connection to an independent land pattern that is electrically unconnected also does not cause any problem.

All the power lines are electrically separated.

And, all the GND pins are connected via the substrate in the device.

PRELIMINARY

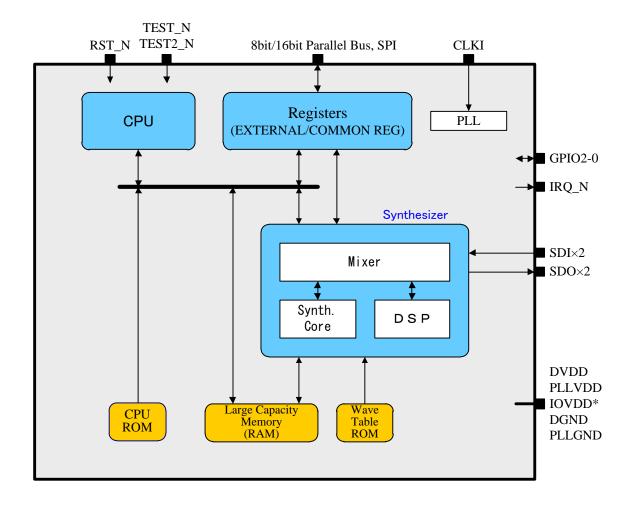

■ Block Diagram

YMW820

# Block Diagram

PRELIMINARY

Block Diagram

YMW820

#### <Registers>

Registers block contains registers and interface circuitry for the host controller communication.

YMW820 supports 8- or 16-bit parallel bus and SPI bus as the host controller interface.

This block also provides access ports for internal YMW820 registers such as COMMON REG, COMMAND FIFO, and the host can read and write those registers through these ports.

#### <CPU>

*CPU* is the integrated data processing application platform based on powerful dual-issue 32-bit RISC processor core and bus-based architecture.

Peripheral functions such as Timer, DMA controller, Interrupt controller are also integrated on chip.

#### <Synthesizer>

*Synthesizer* is the wavetable synthesis core supporting up to 64 simultaneous voices. It also contains DSP for sound effect processing which is controlled from the integrated CPU.

#### <Digital Audio Interface [Input]>

*Digital Audio Interface* block provides two input ports in digital audio interface data format, and these ports can also be used in PCM interface data format.

For digital audio interface data format, it supports input of 16/20/24-bit samples in 2's complement representation at one of 9 sampling rates between 8 kHz and 48 kHz.

For PCM interface data format, it supports 8/13/14/16-bit samples at 8 kHz or 16 kHz sampling rate.

YMW820 can operate as either master or slave input device for both data formats.

As a slave device, it automatically determines and uses one of the 9 supported sampling rates.

Once inside the device, further processing can be applied to these audio samples.

#### <Digital Audio Interface [Output]>

*Digital audio interface* block provides two output ports in digital audio interface data format, and these ports can also be used in PCM interface data format.

For digital audio input interface data format, it supports output of 16/20/24-bit samples in 2's complement representation at one of 9 sampling rates between 8 kHz and 48 kHz.

For PCM interface data format, it supports output of 8/13/14/16-bit samples at 8 kHz or 16 kHz sampling rate.

YMW820 can operate as either master or slave output device for both data formats.

As a slave device, it automatically determines and uses one of the 9 supported sampling rates.

#### <PLL, Clock Generator>

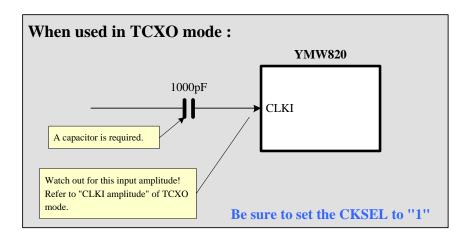

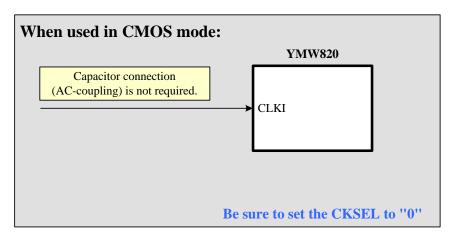

CLKI pin of this block accepts standard CMOS level inputs, and in *TCXO mode* also accepts a low amplitude inputs.

PLL block generates system clocks used in YMW820 from the clock signal on CLKI pin.

# ■ Electrical Characteristics

• Absolute Maximum Ratings

| Parameter                          | Symbol | Min. | Max.       | Unit |

|------------------------------------|--------|------|------------|------|

| DVDD Supply Voltage                | DVDD   | -0.3 | 1.40       | V    |

| PLLVDD Supply Voltage              | PLLVDD | -0.3 | 1.40       | V    |

| IOVDD1 Supply Voltage              | IOVDD1 | -0.3 | 4.20       | V    |

| IOVDD2 Supply Voltage              | IOVDD2 | -0.3 | 4.20       | V    |

| IOVDD3 Supply Voltage              | IOVDD3 | -0.3 | 4.20       | V    |

| Digital Input Voltage(1) (*1) (*4) | VIND1  | -0.3 | IOVDD1+0.3 | V    |

| Digital Input Voltage(2) (*2) (*4) | VIND2  | -0.3 | IOVDD2+0.3 | V    |

| Digital Input Voltage(3) (*3) (*4) | VIND3  | -0.3 | IOVDD3+0.3 | V    |

| Power Dissipation (*5)             | Pd     |      | 203        | mW   |

| Storage Temperature                | TSTG   | -50  | 125        | °C   |

[Conditions] DGND = PLLGND = 0 V

- (\*1) For input pins and input/output pins that run from IOVDD1 supply.

- (\*2) For input pins and input/output pins that run from IOVDD2 supply.

- (\*3) For input pins and input/output pins that run from IOVDD3 suppy.

- (\*4) The value is applicable even if the supply voltages are outside the recommended operationg range.

- e.g., When power supply pins are at 0 V, voltages over 0.3 V do not meet the rating.

- (\*5) For Top = 25°C, PCB (76.2 mm × 114.3 mm × 1.6 tmm), glass-reinforced epoxy PCB board.

When operating above Top =  $25^{\circ}$ C, derate the value by 2.03 mW per  $1^{\circ}$ C.

The value is of approximate nature, as it was obtained by a simulation program assuming a certain condition.

Recommended Operating Conditions

| Parameter                           | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------|------|------|------|------|

| DVDD, PLLVDD Operating Voltage (*1) | DVDD   | 1.02 | 1.10 | 1.20 | V    |

| IOVDD1 Operating Voltage            | IOVDD1 | 1.65 | 1.80 | 3.60 | V    |

| IOVDD2 Operating Voltage            | IOVDD2 | 1.65 | 1.80 | 3.60 | V    |

| IOVDD3 Operating Voltage            | IOVDD3 | 1.65 | 1.80 | 3.60 | V    |

| Operating Ambient Temperature       | TOP    | -20  | 25   | 85   | °C   |

[Conditions] DGND = PLLGND = 0 V

(\*1) PLLVDD must be connected to DVDD through a discrete resistor external to YMW820.

Power Consumptions

| Parameter            | Condition                    | Typ. (*1) | Max. (*2) | Unit |

|----------------------|------------------------------|-----------|-----------|------|

|                      | Normal Operation (*4)        |           |           |      |

| DVDD + PLLVDD        | (CPU_FREQ="0")               | 35        |           | mA   |

|                      | (CPU_FREQ="1")               | 25        |           |      |

| IOVDD1               | Normal Operation (*4)        | 0.5       |           | mA   |

| IOVDD2               | Normal Operation (*5)        | 0.8       |           | mA   |

| IOVDD3               | Normal Operation (CMOS mode) | 0.1       |           | mA   |

|                      | Normal Operation (TCXO mode) | 0.1       |           | mA   |

| Power-off mode (*3)  | Total power supply current   | 20        | 60        | μΑ   |

| Power-save mode (*3) | Total power supply current   | 450       | 1800      | μΑ   |

- (\*1) With the typical values of voltages specified in the recommended operating conditions, and at TOP = 25°C.

- (\*2) With the maximum values of voltages specified in the recommended operating conditions, and at TOP = 25°C.

- $(*3)\ ECS\_N\ input\ pin\ (V_{IH}\ =\ IOVDD1\ fixed);\ other\ input\ pins\ (V_{IL}\ =\ DGND,\ V_{IH}\ =\ IOVDD1,\ IOVDD2,\ IOVDD3)$

- (\*4) For playback of sample sound contents using the on-chip GM sound presets as well as high-quality waveforms downloaded from the host on the on-chip wave memory.

- (\*5) DIR, DIT setting: fs = 48.0 kHz, BCLK = 64 fs, Master mode

#### • DC characteristics

| Parameter                             | Symbol           | Condition                         | Min.                 | Тур.                        | Max.                 | Unit |

|---------------------------------------|------------------|-----------------------------------|----------------------|-----------------------------|----------------------|------|

| Input Voltage "H" Level 1             | $V_{IH}$         | (*1)                              | $0.70 \times IOVDD1$ |                             |                      | V    |

| Input Voltage "L" Level 1             | $V_{\rm IL}$     | (*1)                              |                      |                             | $0.30 \times IOVDD1$ | V    |

| Input Voltage "H" Level 2             | $V_{IH}$         | (*2)                              | $0.70 \times IOVDD2$ |                             |                      | V    |

| Input Voltage "L" Level 2             | $V_{\rm IL}$     | (*2)                              |                      |                             | $0.30 \times IOVDD2$ | V    |

| Input Voltage "H" Level 3             | $V_{IH}$         | (*3)                              | $0.75 \times IOVDD2$ |                             |                      | V    |

| Input Voltage "L" Level 3             | $V_{\rm IL}$     | (*3)                              |                      |                             | $0.25 \times IOVDD2$ | V    |

| Input Voltage "H" Level 4             | $V_{IH}$         | (*4)                              | $0.75 \times IOVDD3$ |                             |                      | V    |

| Input Voltage "L" Level 4             | $V_{\rm IL}$     | (*4)                              |                      |                             | $0.25 \times IOVDD3$ | V    |

| Output Voltage "H" Level 1            | $V_{OH}$         | (*1) (*5)                         | $0.80 \times IOVDD1$ |                             |                      | V    |

| Output Voltage "L" Level 1            | $V_{OL}$         | (*1) (*5)                         |                      |                             | $0.20 \times IOVDD1$ | V    |

| Output Voltage "H" Level 2            | $V_{OH}$         | (*2) (*5)                         | $0.80 \times IOVDD2$ |                             |                      | V    |

| Output Voltage "L" Level 2            | $V_{OL}$         | (*2) (*5)                         |                      |                             | $0.20 \times IOVDD2$ | V    |

| Schmitt Trigger Trip Point<br>Range 1 | $V_{sh1}$        | TEST_N, TEST2_N,<br>RST_N,<br>RXD |                      | $0.05 \times \text{IOVDD2}$ |                      | V    |

| Schmitt Trigger Trip Point<br>Range 2 | $V_{\text{sh2}}$ | CLKI (*4)                         |                      | $0.05 \times IOVDD3$        |                      | V    |

| Input Leakage Current                 | IL               |                                   | ·                    |                             | ±1.0                 | μΑ   |

| Input Capacitance                     | CI               |                                   |                      |                             | 10                   | pF   |

$[Conditions] \quad \text{With the Recommended Operating Conditions, and capacitive load of 50 pF.} \\$

- (\*1) For pins running from IOVDD1 supply.

- (\*2) For pins: SDI\*, LRCK\*, BCLK\*, GPIO\*.

- (\*3) For pins: RST\_N, TEST\_N, TEST2\_N, RXD.

- (\*4) For pins: CLKI (in CMOS mode).

- (\*5) For BCLK\*, GPIO\*:  $I_{OH} = -2$  mA,  $I_{OL} = +2$  mA, other output pins:  $I_{OH} = -1$  mA,  $I_{OL} = +1$  mA. For other output pins:  $I_{OH} = -0.2$  mA,  $I_{OL} = +0.2$  mA (when IOVDD1, IOVDD2 is less than 2.20 V)

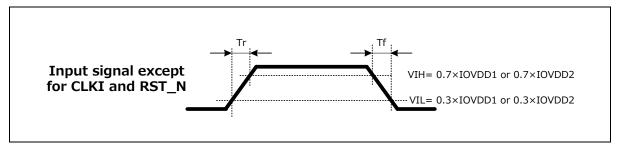

#### • AC Characteristics

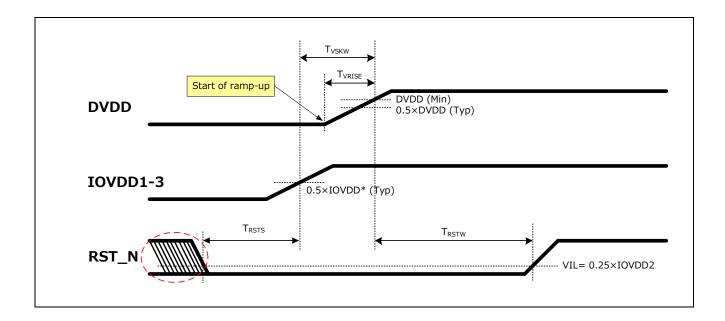

#### Power Up and Reset Sequences, and Input Signal Rise/Fall Time

| Parameter                                             | Symbol         | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|----------------|------|------|------|------|

| RST_N "L" pulse width (*1)                            | $T_{RSTW}$     | 1    |      |      | μs   |

| RST_N setup (for undefined $\rightarrow$ L) time (*2) | $T_{RSTS}$     | 0    |      |      | μs   |

| Power supply ramp time (*3)                           | $T_{ m VRISE}$ |      |      | 10   | ms   |

| Power-up timing skew between power supplies (*4)      | $T_{VSKW}$     | 0    |      | 5    | ms   |

| Rise and fall time of inputs except CLKI, RST_N       | $T_r, T_f$     |      |      | 20   | ns   |

[Conditions] With the Recommended Operating Conditions.

- (\*1) This value is specified for the timing of RST\_N signal and the last supply to become valid among DVDD, IOVDD1 through 3. The timing of PLLVDD is outside the consideration.

- (\*2) Specified for the timings of IOVDD2 ramp-up and RST\_N signal.

- (\*3) Specified the ramp time for power supplies.

(It is the time from the start of supply until the minimum voltage in the Recommended Operating Condition is reached.) Diagram below shows only DVDD timing, although the specification applies to IOVDD1 through 3.

- (\*4) This value is specified for the ramp-up timings of the first and the last supplies to become valid among DVDD and IOVDD1 through 3.

#### **Timing Diagram For When IOVDD\* Comes up Before DVDD**

Power sequencing among DVDD and IOVDDs supplies is not specified for this device. In timing diagram below IOVDDs come up before DVDD (and IOVDD1 through 3 come up at the same time).

- DVDD (Min.) is the minimum value specified in the Recommended Operating Conditions.

- DVDD (Typ.) and IOVDD\* (Typ.) are the typical values specified in the Recommended Operating Conditions.

- RST\_N signal must stay within the range specified in the Absolute Maximum Ratings even while the signal is not driven and the device is not powered.

- (\*) Although particular power sequencing is not required, we recommend the following.

**YMW820**

- 1. Turn on IOVDDs. (No particular order requested for IOVDD1 through IOVDD3)

- 2. Turn on DVDD.

- 3. Release the reset signal (RST $_N =$ "H").

## Notes on RST\_N signal during power supply ramp-up

RST\_N pin must be driven low when IOVDD2 supply ramps up or earlier.

IO directions of the bidirectional pins that run from IOVDD2 supply and output levels of the output pins that run from IOVDD2 supply get ready when RST\_N is low and IOVDD2 reach its valid range.

IO directions of ED15 through ED0 pins get set by the logic levels of ECS\_N and ERD\_N which run from IOVDD1 supply. (The levels of ECS\_N and ERD\_N do not affect the direction of ED15 through ED8 which always become input pins when ECPU8BIT is high, that is, when the bus width is 8-bit) IO directions of ED15-ED0 get set with valid IOVDD1 even before DVDD ramps up. (ECS\_N is recommended to be driven low when IOVDD1 ramps up).

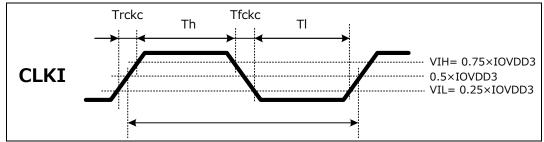

#### • Clock Input (CLKI)

#### i) CMOS Mode

| Parameter                            | Symbol       | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------------|------|------|------|------|

| CLKI frequency                       | 1 / Tfreq    | 10   |      | 27   | MHz  |

| CLKI rise / fall time                | Trckc, Tfckc |      |      | 30   | ns   |

| CLKI high time                       | Th           | 15   |      |      | ns   |

| CLKI low time                        | Tl           | 15   |      |      | ns   |

| Acceptable frequency deviation range | -            |      |      | ±100 | ppm  |

[Conditions] With the Recommended Operating Conditions.

Clock signals to CLKI can be stopped (= 0 Hz) and fixed to a level in Power-off and Power-save mode, and during the device reset.

$\boldsymbol{\cdot}$  When DVDD and IOVDDs come from different supplies, ramp up DVDD first.

#### **■** Electrical Characteristics

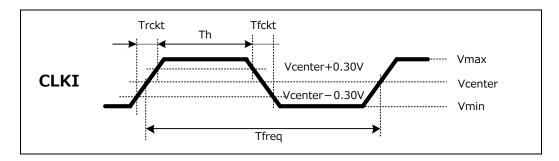

#### ii) TCXO Mode

| Parameter                            | Symbol         | Min. | Тур. | Max.            | Unit |

|--------------------------------------|----------------|------|------|-----------------|------|

| CLKI frequency                       | 1 / Tfreq      | 10   |      | 27              | MHz  |

| CLKI rise/ fall time                 | Trckt, Tfckt   |      |      | 50              | ns   |

| CLKI amplitude H (*1)                | Vmax - Vcenter | 0.20 |      | 0.35×<br>IOVDD3 | V    |

| CLKI amplitude L (*1)                | Vcenter-Vmin   | 0.20 |      | 0.35×<br>IOVDD3 | V    |

| Wait time to stable (*1)             | Twait          | 2    |      |                 | ms   |

| Feedback resistance                  | Rck            | 13.5 | 27   | 54              | kΩ   |

| Acceptable frequency deviation range | -              |      |      | ±100            | ppm  |

[Conditions] With the Recommended Operating Conditions.

(\*1) TCXO module's output is assumed to be AC-coupled to CLKI using a 1000 pF capacitor.

The AC-coupling capacitor must be 1000 pF for this application.

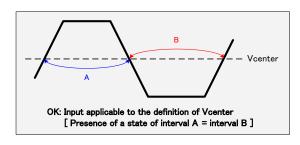

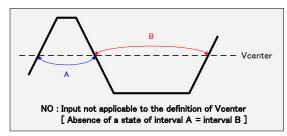

• *Vcenter* is defined as the voltage level of TCXO signals at which the duty cycles of CLKI become 50% (High time = Low time).

When Vcenter cannot be defined as above for a waveform, for example, when there are too much high/low time disparities, the use of such waveforms as CLKI is prohibited.

- Trckt and Tfckt are specified as a transition time between the two reference signal levels, Vcenter + 0.30 [V] and Vcenter 0.30 [V].

- Tfreq is specified as a cycle period using the reference level at Vcenter (Duty = 50%).

#### iii) Design note on CLKI clock input networks

CKSEL configures if YMW820 operates in TCXO mode or CMOS mode.

Notice that external networks for CLKI pin and the expected clock signal characteristics are different for each mode. Section *Clock Input (CLKI)* for the signal characteristics.

Refer to "Input Clock (CLKI)" for the details of the characteristics of CLKI pin's input signals.

CKSEL configuration, and the external network and the expected clock signal characteristics on CLKI pin must be consistent with each other.

#### • Host Controller Interface Timing (8-bit, 16-bit parallel bus)

Followings are the conditions assumed for the specified values.

$Input \ logic \ voltage \ levels \\ \hspace*{0.2in} : V_{IH} = 0.80 \times IOVDD1, \ V_{IL} = 0.20 \times IOVDD1$

Input, output timing reference levels :  $V_{IH} = 0.70 \times IOVDD1$ ,  $V_{IL} = 0.30 \times IOVDD1$

$V_{OH} = 0.70 \times IOVDD1, V_{OL} = 0.30 \times IOVDD1$

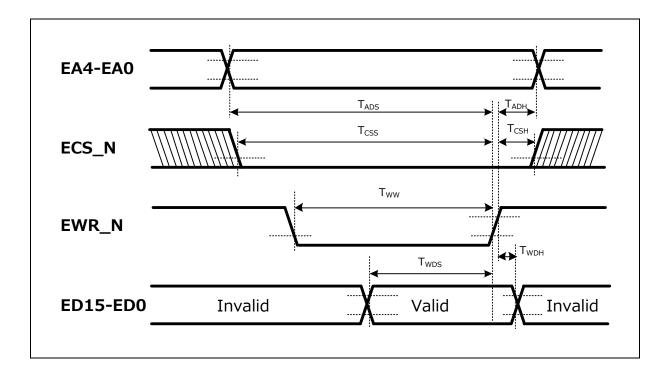

#### Write Cycle

| Parameter              | Symbol             | Min. | Max. | Unit |

|------------------------|--------------------|------|------|------|

| Address setup time     | $T_{ADS}$          | 30   |      | ns   |

| Address hold time      | $T_{\mathrm{ADH}}$ | 0    |      | ns   |

| Chip select setup time | T <sub>CSS</sub>   | 30   |      | ns   |

| Chip select hold time  | $T_{CSH}$          | 0    |      | ns   |

| Write pulse width      | $T_{ m WW}$        | 30   |      | ns   |

| Data setup time        | $T_{ m WDS}$       | 20   |      | ns   |

| Data hold time         | $T_{ m WDH}$       | 0    |      | ns   |

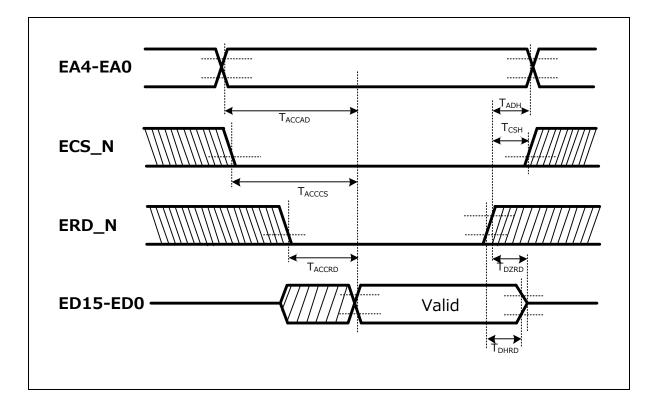

#### Read Cycle

| Parameter                             |                 | Symbol              | Min. | Max. | Unit |

|---------------------------------------|-----------------|---------------------|------|------|------|

| Address hold time                     |                 | $T_{ m ADH}$        | 0    |      | ns   |

| Chip select hold time                 |                 | $T_{CSH}$           | 0    |      | ns   |

| Access time from ERD_N pin            |                 |                     |      |      |      |

|                                       | (ECPU_DRVS="0") | $T_{ACCRD}$         |      | 50   | ns   |

|                                       | (ECPU_DRVS="1") |                     |      | 60   |      |

| Access time from ECS_N pin            |                 |                     |      |      |      |

|                                       | (ECPU_DRVS="0") | $T_{ACCCS}$         |      | 50   | ns   |

|                                       | (ECPU_DRVS="1") |                     |      | 70   |      |

| Access time from EA4 - EA0 pin        |                 |                     |      |      |      |

|                                       | (ECPU_DRVS="0") | $T_{ACCAD}$         |      | 50   | ns   |

|                                       | (ECPU_DRVS="1") |                     |      | 60   |      |

| Data hold time from ERD_N pin         |                 | $T_{\mathrm{DHRD}}$ | 0    |      | ns   |

| High-impedance transition time from E | RD_N pin        | $T_{\mathrm{DZRD}}$ |      | 15   | ns   |

[Conditions] With the Recommended Operating Conditions, and capacitive load of 50 pF  $I_{OH},\,I_{OL}=0\ mA$

■ Electrical Characteristics YMW820

#### i) Timing Diagram for Write Operations

#### Notes:

T<sub>ADH</sub> : EA4-EA0 hold time relative to the 0.70×IOVDD1 reference timing point of rising EWR\_N

assuming both  $T_{\text{CSH}}$  and  $T_{\text{WDH}}$  meet the minimum value of  $0\ \text{ns}.$

$T_{CSH}$  : ECS\_N hold time relative to the 0.70×IOVDD1 reference timing point of rising EWR\_N

assuming both  $T_{\text{ADH}}$  and  $T_{\text{WDH}}$  meet the minimum value of  $0\ \text{ns}.$

$T_{WDH}$  : ED15-ED0 hold time relative to the 0.70×IOVDD1 reference timing point of rising

$EWR\_N$  assuming both  $T_{ADH}$  and  $T_{WDH}$  meet the minimum value of  $0\ ns.$

$T_{ADS} \hspace{0.5cm} : \hspace{0.5cm} EA4\text{-}EA0 \hspace{0.1cm} setup \hspace{0.1cm} time \hspace{0.1cm} relative \hspace{0.1cm} to \hspace{0.1cm} the \hspace{0.1cm} 0.30\times IOVDD1 \hspace{0.1cm} reference \hspace{0.1cm} timing \hspace{0.1cm} point \hspace{0.1cm} of \hspace{0.1cm} rising \hspace{0.1cm} EWR\_N$

assuming all of T<sub>CSS</sub>, T<sub>WW</sub>, and T<sub>WDS</sub> meet the minimum value.

$T_{CSS}$  : ECS\_N setup time relative to the 0.30×IOVDD1 reference timing point of rising EWR\_N

assuming all of  $T_{ADS}$ ,  $T_{WW}$ , and  $T_{WDS}$  meet the minimum value.

■ Electrical Characteristics YMW820

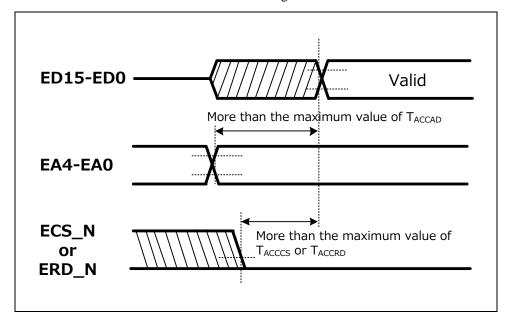

#### ii) Timing Diagram for Read Operations

Notes:

$T_{ACCAD}$ : Access time from EA4-EA0 reaching 0.70×IOVDD1 or 0.30×IOVDD1, to ED15-ED0 reaching 0.70×IOVDD1 or 0.30×IOVDD1, assuming ERD\_N and ECS\_N become valid *in time* (\*1).

T<sub>ACCCS</sub>: Access time from ECS\_N reaching 0.30×IOVDD1, to ED15-ED0 reaching 0.70×IOVDD1 or 0.30×IOVDD1, assuming EA4-EA0and ERD\_N become valid *in time* (\*1).

$T_{ACCRD}$ : Access time from ERD\_N reaching 0.30×IOVDD1, to ED15-ED0 reaching 0.70×IOVDD1 or 0.30×IOVDD1, assuming EA4-EA0 and ECS\_N become valid *in time* (\*1).

$T_{DHRD}$ : ED15-ED0 hold time relative to the 0.30×IOVDD1 reference timing point of rising ERD\_N assuming both  $T_{ADH}$  and  $T_{CSH}$  are 0 ns or more.

$T_{DZRD}$ : ED15-ED0 transition time, into the high impedance states, relative to the  $0.70 \times IOVDD1$  reference timing point of rising ERD\_N assuming both  $T_{ADH}$  and  $T_{CSH}$  are 0 ns or more.

**YMW820**

#### (\*1) in time Means:

For ECS\_N : ECS\_N has reached  $0.30 \times IOVDD1 T_{ACCCS}$  or more before ED15-ED0 all

reaching  $0.70 \times IOVDD1$  or  $0.30 \times IOVDD1$ .

For ERD\_N : ERD\_N has reached  $0.30 \times IOVDD1\ T_{ACCRD}$  or more before ED15-ED0 all

reaching  $0.70 \times IOVDD1$  or  $0.30 \times IOVDD1$ .

For EA4-EA0 : EA4-EA0 have reached  $0.70 \times IOVDD1$  or  $0.30 \times IOVDD1$   $T_{ACCAD}$  or more

before ED15-ED0 all reaching  $0.70 \times IOVDD1$  or  $0.30 \times IOVDD1$ .

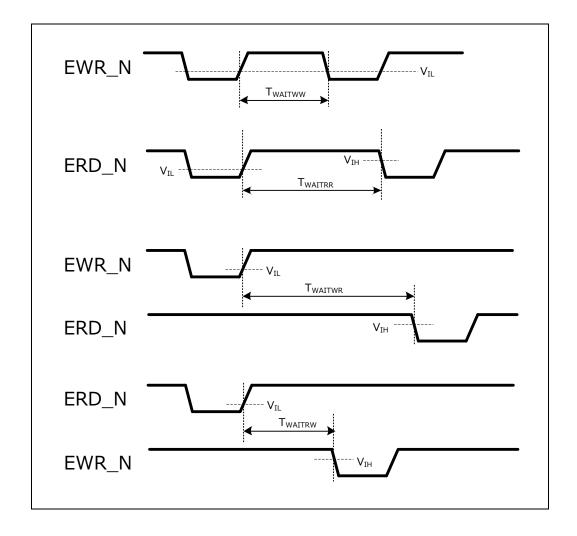

#### iii) Access Wait State

| Parameter                               | Symbol       | Min. | Max. | Unit |

|-----------------------------------------|--------------|------|------|------|

| Write – Write access sequence wait time |              |      |      |      |

| (First write after software RESET) (*1) | $T_{WAITWW}$ | 200  |      | ns   |

| (Other than above)                      | $T_{WAITWW}$ | 30   |      | ns   |

| Read – Read access sequence wait time   | $T_{WAITRR}$ | 120  |      | ns   |

| Write – Read access sequence wait time  |              |      |      |      |

| (First read after software RESET) (*1)  | $T_{WAITWR}$ | 150  |      | ns   |

| (Other than above)                      | $T_{WAITWR}$ | 120  |      | ns   |

| Read – Write access sequence wait time  | $T_{WAITRD}$ | 30   |      | ns   |

<sup>(\*1)</sup> Wait time for the first read or write operation following a write to EXTERNAL REG 0x0E RESET.

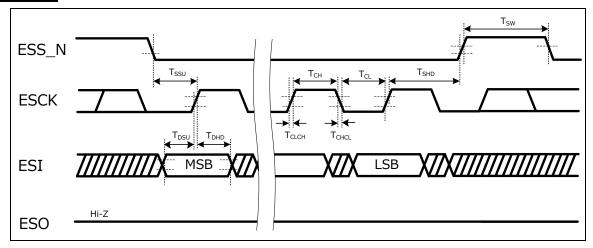

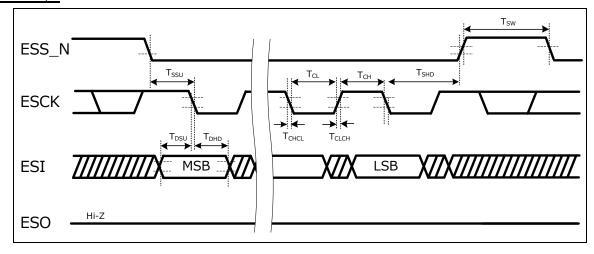

#### Host Controller Interface Timing (SPI)

Followings are the conditions assumed for the specified values.

$Input \ logic \ voltage \ levels \\ \hspace*{0.2in} : V_{IH} = 0.80 \times IOVDD1, \ V_{IL} = 0.20 \times IOVDD1$

Input, output timing reference levels :  $V_{IH} = 0.70 \times IOVDD1$ ,  $V_{IL} = 0.30 \times IOVDD1$

$V_{OH}\!=\!\!0.70\times IOVDD1,\,V_{OL}\!\!=\!\!0.30\times IOVDD1$

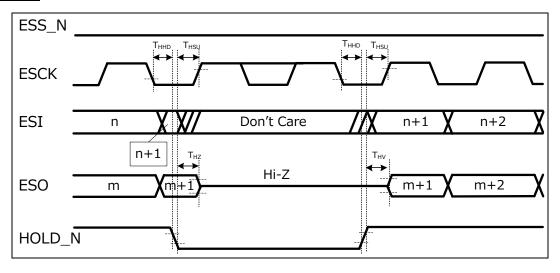

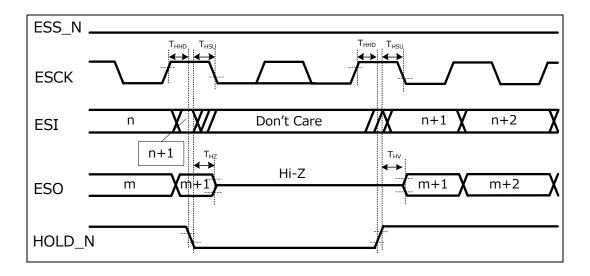

#### Input timing

| Parameter                          |                 | Symbol       | Min. | Max. | Unit |

|------------------------------------|-----------------|--------------|------|------|------|

| ESCK frequency (Write access) (*1) |                 | $F_{C}$      |      | 40   | MHz  |

| ESCK frequency (Read access) (*1)  |                 |              |      |      |      |

|                                    | (ECPU_DRVS="0") | $F_{CR}$     |      | 15   | MHz  |

|                                    | (ECPU_DRVS="1") |              |      | 10   |      |

| ESCK "H" pulse width               |                 | $T_{CH}$     | 10   |      | ns   |

| ESCK "L" pulse width               |                 | $T_{CL}$     | 10   |      | ns   |

| ESCK rise time (*1)                |                 | $T_{CLCH}$   |      | 5    | ns   |

| ESCK fall time (*1)                |                 | $T_{CHCL}$   |      | 5    | ns   |

| ESS_N setup time                   |                 | $T_{SSU}$    | 15   |      | ns   |

| ESS_N hold time                    |                 | $T_{SHD}$    | 15   |      | ns   |

| ESI setup time                     |                 | $T_{ m DSU}$ | 5    |      | ns   |

| ESI hold time                      |                 | $T_{ m DHD}$ | 10   |      | ns   |

| HOLD_N setup time                  |                 | $T_{ m HSU}$ | 10   |      | ns   |

| HOLD_N hold time                   |                 | $T_{ m HHD}$ | 10   |      | ns   |

| ESS_N "H" pulse width              |                 | $T_{SW}$     | 20   |      | ns   |

<sup>(\*1)</sup> Maximum ESCK rise time and fall time cannot be made to fit the cycle period for the maximum ESCK frequency.

#### Output timing

| Parameter                                   | Symbol            | Min. | Max. | Unit |

|---------------------------------------------|-------------------|------|------|------|

| Access time                                 |                   |      |      |      |

| (ECPU_DRVS="0")                             | $T_{QV}$          |      | 30   | ns   |

| (ECPU_DRVS="1")                             |                   |      | 40   |      |

| Data hold time                              | $T_{QX}$          | 2    |      | ns   |

| High-impedance transition time              | $T_{\mathrm{QZ}}$ |      | 10   | ns   |

| Access time (HOLD_N="L")                    |                   |      |      |      |

| (ECPU_DRVS="0")                             | $T_{\mathrm{HV}}$ |      | 30   | ns   |

| (ECPU_DRVS="1")                             |                   |      | 40   |      |

| High-impedance transition time (HOLD_N="L") | $T_{ m HZ}$       |      | 15   | ns   |

[Conditions] With the Recommended Operating Conditions, and capacitive load of 30 pF  $I_{OH}$  = -2 mA,  $I_{OL}$  = +2 mA

YMW820

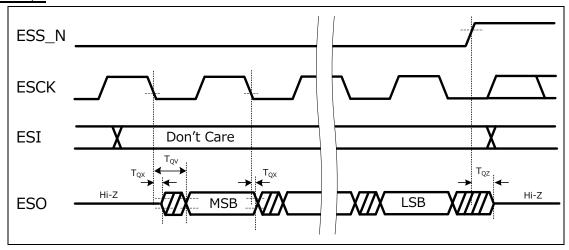

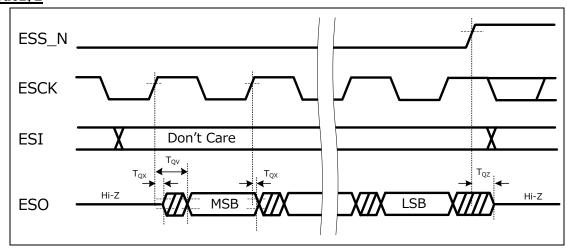

# Timing Diagram for Serial Input Operations

## Mode 0, 3

## Mode 1, 2

YMW820

# Timing Diagram for Serial Output Operations

## Mode 0, 3

# <u>Mode1, 2</u>

## Timing Diagram for Hold Operations

### **Mode 0, 3**

# Mode 1, 2

#### **■** Electrical Characteristics

# Digital Audio Interface Timing

Followings are the conditions assumed for the specified values.

Input logic voltage levels :  $V_{IH} = 0.80 \times IOVDD2$ ,  $V_{IL}=0.20 \times IOVDD2$

Input, output timing reference levels :  $V_{IH} = 0.70 \times IOVDD2$ ,  $V_{IL} = 0.30 \times IOVDD2$

$V_{OH}$  =0.70 × IOVDD2,  $V_{OL}$ =0.30 × IOVDD2

**YMW820**

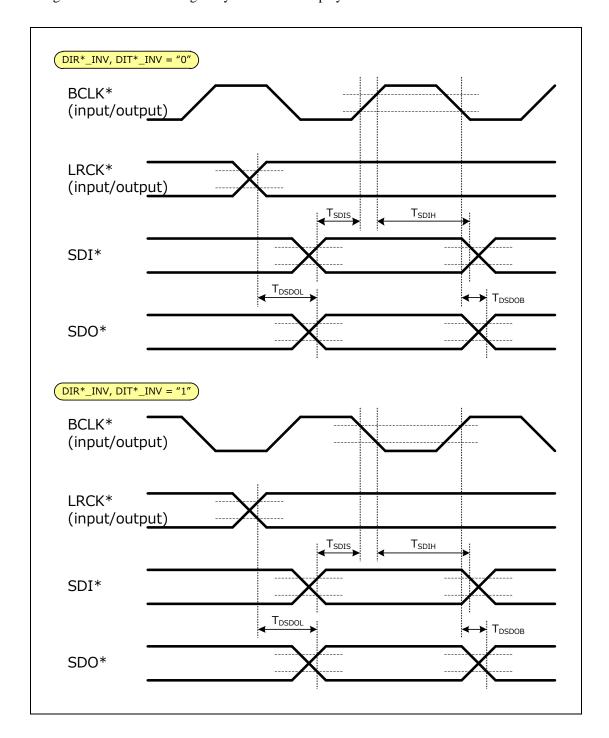

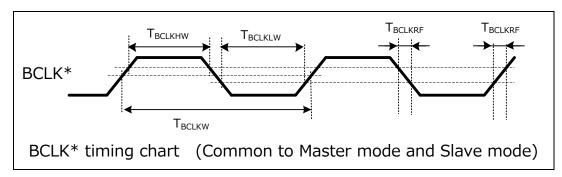

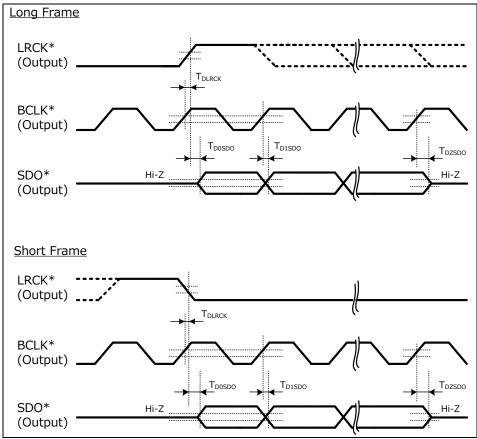

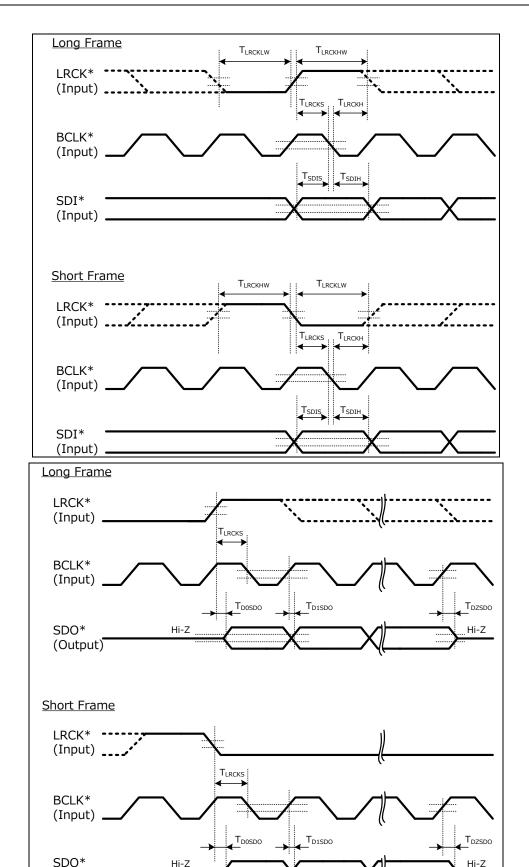

### i) Common to Master Mode and Slave Mode

| Parameter                                  | Symbol         | Min. | Тур. | Max. | Unit |

|--------------------------------------------|----------------|------|------|------|------|

| SDI input setup time                       | $T_{ m SDIS}$  | 65   |      |      | ns   |

| SDI input hold time                        | $T_{SDIH}$     | 65   |      |      | ns   |

| SDO output delay time                      |                |      |      |      |      |

| (Of the first bit after LRCK toggles) (*4) | $T_{ m DSDOL}$ | 0    |      | 65   | ns   |

| (Other than above) (*4)                    | $T_{DSDOB}$    | 0    |      | 65   | ns   |

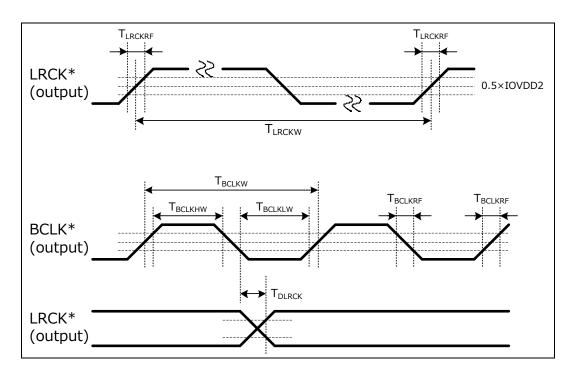

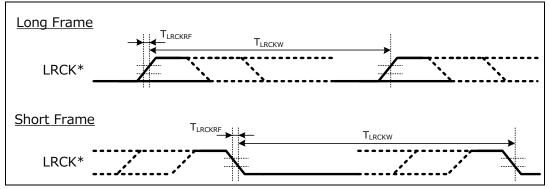

#### ii) Master Mode

| Parameter                      | Symbol                 | Min. | Тур.                                                                      | Max. | Unit |

|--------------------------------|------------------------|------|---------------------------------------------------------------------------|------|------|

| BCLK output frequency (*2)(*3) | 1 / T <sub>BCLKW</sub> |      | 64fs_ <sub>DA</sub><br>48fs_ <sub>DA</sub><br>32fs_ <sub>DA</sub><br>(*1) |      | kHz  |

| BCLK output "H" time           | $T_{BCLKHW}$           | 120  |                                                                           |      | ns   |

| BCLK output "L" time           | $T_{BCLKLW}$           | 120  |                                                                           |      | ns   |

| BCLK output rise / fall time   | $T_{BCLKRF}$           |      |                                                                           | 20   | ns   |

| LRCK output frequency (*3)     | 1 / T <sub>LRCKW</sub> |      | fs_DA(*1)                                                                 |      | kHz  |

| LRCK output delay time         | $T_{DLRCK}$            | -50  |                                                                           | 50   | ns   |

| LRCK output rise / fall time   | $T_{LRCKRF}$           |      |                                                                           | 20   | ns   |

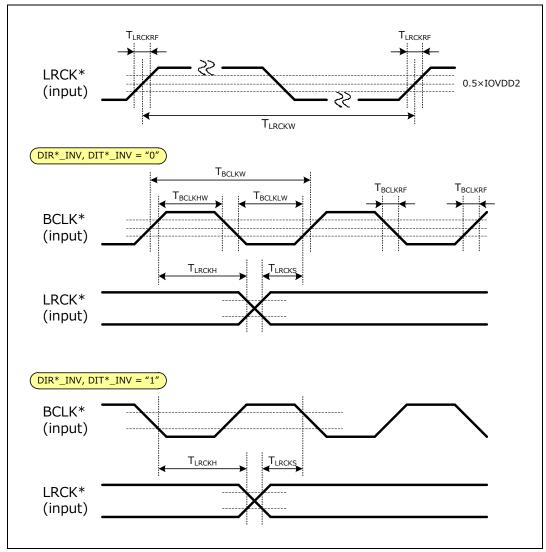

#### iii) Slave Mode

| Parameter                   | Symbol                 | Min. | Тур.                                  | Max. | Unit |

|-----------------------------|------------------------|------|---------------------------------------|------|------|

| BCLK input frequency        | 1 / T <sub>BCLKW</sub> |      | 64fs_DA<br>48fs_DA<br>32fs_DA<br>(*1) |      | kHz  |

| BCLK input "H" time         | $T_{BCLKHW}$           | 120  |                                       |      | ns   |

| BCLK input "L" time         | $T_{BCLKLW}$           | 120  |                                       |      | ns   |

| BCLK input rise / fall time | $T_{BCLKRF}$           |      |                                       | 20   | ns   |

| LRCK input frequency        | 1 / T <sub>LRCKW</sub> |      | fs_ <sub>DA</sub> (*1)                |      | kHz  |

| LRCK input setup time       | $T_{LRCKS}$            | 65   |                                       |      | ns   |

| LRCK input hold time        | $T_{LRCKH}$            | 65   |                                       |      | ns   |

| LRCK input rise / fall time | $T_{LRCKRF}$           |      |                                       | 20   | ns   |

**YMW820**

[Conditions] With the Recommended Operating Conditions, and capacitive load of 30 pF

$I_{OH}\!=\!-1.0~\text{mA},\quad I_{OL}\!=\!+1.0~\text{mA}~(IOVDD\geq2.20~\text{V})$

$I_{OH} = -0.2 \text{ mA}, \quad I_{OL} = +0.2 \text{ mA (IOVDD} < 2.20 \text{ V)}$

- $(*1)~\text{fs}_{\text{DA}}$  is the sampling frequency of the digital audio interface.

- (\*2) BCLK outputs have jitters from logic operations.

- (\*3) Clocks may not be at the exact frequency for particular CLKI frequency and PLL settings.

- (\*4) The value for (Other than above) case apply all the time for I2S format timing.

# Incoming (LRCK) Frequency Range Limitation

As a slave mode device, the input frequency of LRCK has limited range.

Using LRCK outside this range may result in failed playbacks.

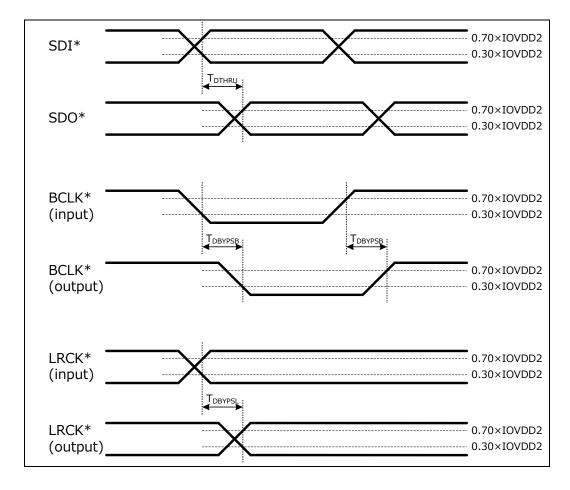

#### iv) Transit Time in Bypass Mode

These are the transit time when the interface is in bypass mode.

| Parameter                 | Symbol                | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------------|------|------|------|------|

| SDI→SDO output delay time | $T_{\mathrm{DTHRU}}$  |      |      | 50   | ns   |

| BCLK→BCLK delay time      | $T_{\mathrm{DBYPSB}}$ |      |      | 50   | ns   |

| LRCK→LRCK delay time      | $T_{\mathrm{DBYPSL}}$ |      |      | 50   | ns   |

[Conditions] With the Recommended Operating Conditions, and a pacitive load of 30 pF  $\,$

#### **■** Electrical Characteristics

#### PCM Interface Timing

Followings are the conditions assumed for the specified values.

Input logic voltage levels :  $V_{IH} = 0.80 \times IOVDD2$ ,  $V_{IL} = 0.20 \times IOVDD2$

Input, output timing reference levels :  $V_{IH} = 0.70 \times IOVDD2$ ,  $V_{IL} = 0.30 \times IOVDD2$

$V_{OH} = 0.70 \times IOVDD2$ ,  $V_{OL} = 0.30 \times IOVDD2$

#### i) Master Mode

| Parameter                                   | Symbol                        | Min. | Тур.                                                        | Max.     | Unit |

|---------------------------------------------|-------------------------------|------|-------------------------------------------------------------|----------|------|

| SDI input setup time                        | $T_{SDIS}$                    | 65   |                                                             |          | ns   |

| SDI input hold time                         | $T_{\mathrm{SDIH}}$           | 65   |                                                             |          | ns   |

| BCLK output frequency (*2)(*3)              | 1 / T <sub>BCLKW</sub>        |      | 64fs_DA<br>48fs_DA<br>32fs_DA<br>24fs_DA<br>16fs_DA<br>(*1) |          | kHz  |

| BCLK output "H" time                        | $T_{BCLKHW}$                  | 450  |                                                             |          | ns   |

| BCLK output "L" time                        | $T_{BCLKLW}$                  | 450  |                                                             |          | ns   |

| BCLK output rise / fall time                | $T_{BCLKRF}$                  |      |                                                             | 20       | ns   |

| LRCK output frequency                       | 1 / T <sub>LRCKW</sub>        |      | 8, 16                                                       |          | kHz  |

| LRCK output delay time                      | $T_{DLRCK}$                   | -50  |                                                             | 50       | ns   |

| LRCK output rise / fall time                | $T_{LRCKRF}$                  |      |                                                             | 20       | ns   |

| SDO output delay time                       |                               |      |                                                             |          |      |

| (First bit in Slot 0)<br>(Other than above) | $T_{ m D0SDO} \ T_{ m D1SDO}$ | 0    |                                                             | 80<br>80 | ns   |

| SDO High-impedance transition time          | T <sub>DZSDO</sub>            | 0    |                                                             | 60       | ns   |

[Conditions] With the Recommended Operating Conditions, and capacitive load of 30 pF

$I_{OH}\!=\!-1.0~mA,\quad I_{OL}\!=\!+1.0~mA~(IOVDD\!\geq\!2.20V)$

$I_{OH} = -0.2 \text{ mA}, \quad I_{OL} = +0.2 \text{ mA (IOVDD} < 2.20 \text{V})$

<sup>(\*1)</sup> fs\_DA is the sampling frequency of the PCM interface.

<sup>(\*2)</sup> BCLK outputs have jitters from logical operations.

<sup>(\*3)</sup> Clocks may not be at the exact frequency for particular CLKI frequency and PLL settings.

#### ii) Slave Mode

| Parameter                          | Symbol                 | Min. | Тур.                                                      | Max. | Unit          |

|------------------------------------|------------------------|------|-----------------------------------------------------------|------|---------------|

| SDI input setup time               | $T_{SDIS}$             | 65   |                                                           |      | ns            |

| SDI input hold time                | $T_{SDIH}$             | 65   |                                                           |      | ns            |

| BCLK input frequency (*2)          | 1 / T <sub>BCLKW</sub> |      | 16fs_ <sub>DA</sub><br>to<br>256fs_ <sub>DA</sub><br>(*1) |      | kHz           |

| BCLK input "H" time                | $T_{BCLKHW}$           | 90   |                                                           |      | ns            |

| BCLK input "L" time                | $T_{BCLKLW}$           | 90   |                                                           |      | ns            |

| BCLK input rise / fall time        | $T_{BCLKRF}$           |      |                                                           | 20   | ns            |

| LRCK input frequency               | 1 / T <sub>LRCKW</sub> |      | 8, 16                                                     |      | kHz           |

| LRCK input "H" time                | $T_{LRCKHW}$           | 2    |                                                           |      | BCLK<br>cycle |

| LRCK input "L" time                | $T_{LRCKLW}$           | 2    |                                                           |      | BCLK<br>cycle |

| LRCK input setup time              | $T_{LRCKS}$            | 65   |                                                           |      | ns            |

| LRCK input hold time               | $T_{LRCKH}$            | 65   |                                                           |      | ns            |

| LRCK input rise / fall time        | $T_{LRCKRF}$           |      |                                                           | 20   | ns            |

| SDO input delay time               |                        |      |                                                           |      |               |

| (First bit of Slot 0)              | $T_{ m D0SDO}$         | 0    |                                                           | 80   | ns            |

| (Other than above)                 | $T_{\rm D1SDO}$        | 0    |                                                           | 80   |               |

| SDO High-impedance transition time | T <sub>DZSDO</sub>     | 0    |                                                           | 60   | ns            |

[Conditions] With the Recommended Operating Conditions, and capacitive load of 30 pF

# **1** Incoming (LRCK) Frequency Range Limitation

As a slave mode device, the input frequency of LRCK has limited range.

Using LRCK outside this range may result in failed playbacks.

<sup>(\*1)</sup> fs\_DA is the sampling frequency of the PCM interface.

<sup>(\*2)</sup> The (\*3) Clocks may not be at the exact frequency for particular CLKI frequency and PLL settings.

Hi-Z

4MW820A00 34

(Output)

Hi-Z

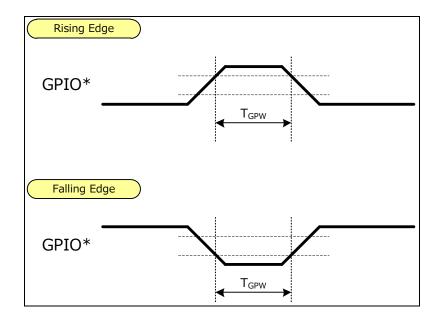

#### GPIO

Followings are the conditions assumed for the specified values.

$\label{eq:logic_voltage} Input logic voltage levels \hspace{1cm} : V_{IH} = 0.80 \times IOVDD2, V_{IL} = 0.20 \times IOVDD2$

Input, output timing reference levels :  $V_{IH} = 0.70 \times IOVDD2$ ,  $V_{IL} = 0.30 \times IOVDD2$

$V_{OH}\!=\!0.70\times IOVDD2,\,V_{OL}\!\!=\!\!0.30\times IOVDD2$

| Parameter               | Symbol             | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------|------|------|------|------|

| Pulse width (Interrupt) | $T_{\mathrm{GPW}}$ | 80   |      |      | ns   |

[Conditions] With the Recommended Operating Conditions.

# **■** Package Information

# U-PK80SP1-01-1

端子厚さ:0.17±0.05 Lead Thickness

カッコ内の寸法値は参考値とします。 The value parenthesized is not specified.

モールド外形寸法はバリを含みません。 Plastic body dimensions do not include burr of resin.

単位 (UNIT): mm (millimeters)

- 注) 1. 表面実装LSIは、保管条件、および、半田付けについての特別な配慮が必要です。

- 2. 組立工場により、寸法や形状などが異なる場合があります。 詳しくはヤマハ代理店までお問い合わせください。

Note: 1. Special attention needs to be paid to the storage conditions and soldering method of the surface mount IC.

2. Dimension, form, etc. may differ depending on assembly plants. For details, please contact your local Yamaha agent.

#### PRECAUTIONS AND INSTRUCTIONS FOR SAFETY

#### WARNING

Prohibited

Do not use the device under stresses beyond those listed in Absolute Maximum Ratings. Such stresses may become causes of breakdown, damages, or deterioration, causing explosion or ignition, and this may lead to fire or personal injury.

Prohibited

Do not mount the device reversely or improperly and also do not connect a supply voltage in wrong polarity. Otherwise, this may cause current and/or power-consumption to exceed the absolute maximum ratings, causing personal injury due to explosion or ignition as well as causing breakdown, damages, or deterioration.

And, do not use the device again that has been improperly mounted and powered once.

Prohibited

Do not short between pins.

In particular, when different power supply pins, such as between high-voltage and low-voltage pins, are shorted, smoke, fire, or explosion may take place.

Instructions

As to devices capable of generating sound from its speaker outputs, please design with safety of your products and system in mind, such as the consequences of unusual speaker output due to a malfunction or failure. A speaker dissipates heat in a voice-coil by air flow accompanying vibration of a diaphragm. When a DC signal (several Hz or less) is input due to device failure, heat dissipation characteristics degrade rapidly, thereby leading to voice-coil burnout, smoking or ignition of the speaker even if it is used within the rated input value.

#### **CAUTION**

Prohibited

Instructions

Generally, semiconductor products may malfunction and break down due to aging, degradation, etc. It is the responsibility of the designer to take actions such as safety design of products and the entire system and also fail-safe design according to applications, so as not to cause property damage and/or bodily injury due to malfunction and/or failure of semiconductor products.

Instructions

The built-in DSP may output the maximum amplitude waveform suddenly due to malfunction from disturbances etc. and this may cause damage to headphones, external amplifiers, and human body (the ear). Please pay attention to safety measures for device malfunction and failure both in product and system design.

Instructions

As semiconductor devices are not nonflammable, overcurrent or failure may cause smoke or fire. Therefore, products should be designed with safety in mind such as using overcurrent protection circuits to control the amount of current during operation and to shut off on failure.

Instructions

Products should be designed with fail safe in mind in case of malfunction of the built-in protection circuits. Note that the built-in protection circuits such as overcurrent protection circuit and high-temperature protection circuit do not always protect the internal circuits. In some cases, depending on usage or situations, such protection circuit may not work properly or the device itself may break down before the protection circuit kicks in.

Use a robust power supply.

Instructions

The use of an unrobust power supply may lead to malfunctions of the protection circuit, causing device breakdown, personal injury due to explosion, or smoke or fire.

Instructions

Product's housing should be designed with the considerations of short-circuiting between pins of the mounted device due to foreign conductive substances (such as metal pins etc.). Moreover, the housing should be designed with spatter prevention etc. due to explosion or burning. Otherwise, the spattered substance may cause bodily injury.

Instructions

The device may be heated to a high temperature due to internal heat generation during operation. Therefore, please take care not to touch an operating device directly.

v02

#### IMPORTANT NOTICE

- YAMAHA RESERVES THE RIGHT TO MAKE CHANGES TO ITS PRODUCTS AND TO THIS DOCUMENT WITHOUT NOTICE. THE INFORMATION CONTAINED IN THIS DOCUMENT HAS BEEN CAREFULLY CHECKED AND IS BELIEVED. HOWEVER, YAMAHA SHALL ASSUME NO RESPONSIBILITIES FOR INACCURACIES AND MAKE NO COMMITMENT TO UPDATE OR TO KEEP CURRENT THE INFORMATION CONTAINED IN THIS DOCUMENT.

- 2. THESE YAMAHA PRODUCTS ARE DESIGNED ONLY FOR COMMERCIAL AND NORMAL INDUSTRIAL APPLICATIONS, AND ARE NOT SUITABLE FOR OTHER USES, SUCH AS MEDICAL LIFE SUPPORT EQUIPMENT, NUCLEAR FACILITIES, CRITICAL CARE EQUIPMENT OR ANY OTHER APPLICATION THE FAILURE OF WHICH COULD LEAD TO DEATH, PERSONAL INJURY OR ENVIRONMENTAL OR PROPERTY DAMAGE. USE OF THE PRODUCTS IN ANY SUCH APPLICATION IS AT THE CUSTOMER'S OWN RISK AND EXPENSE.

- 3. YAMAHA SHALL ASSUME NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCT.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF PRODUCTS. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMES OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND ITILE.

- 6. YAMAHA MAKES EVERY EFFORT TO IMPROVE THE QUALITY AND RELIABILITY OF ITS PRODUCTS. HOWEVER, ALL SEMICONDUCTOR PRODUCTS FAIL WITH SOME PROBABILITY. THEREFORE, YAMAHA REQUIRES THAT SUFFICIENT CARE BE GIVEN TO ENSURING SAFE DESIGN IN CUSTOMER PRODUCTS SUCH AS REDUNDANT DESIGN, ANTI-CONFLAGRATION DESIGN, AND DESIGN FOR PREVENTING MALFUNCTION IN ORDER TO PREVENT ACCIDENTS RESULTING IN INJURY OR DEATH, FIRE OR OTHER SOCIAL DAMAGE FROM OCCURRING AS A RESULT OF PRODUCT FAILURE.

- 7. INFORMATION DESCRIBED IN THIS DOCUMENT: APPLICATION CIRCUITS AND ITS CONSTANTS AND CALCULATION FORMULAS, PROGRAMS AND CONTROL PROCEDURES ARE PROVIDED FOR THE PURPOSE OF EXPLAINING TYPICAL OPERATION AND USAGE. THEREFORE, PLEASE EVALUATE THE DESIGN SUFFICIENTLY AS WHOLE SYSTEM UNDER THE CONSIDERATION OF VARIOUS EXTERNAL OR ENVIRONMENTAL CONDITIONS AND DETERMINE THEIR APPLICATION AT THE CUSTOMER'S OWN RISK. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR CLAIMS, DAMAGES, COSTS AND EXPENSES CAUSED BY THE CUSTOMER OR ANY THIRD PARTY, OWING TO THE USE OF THE ABOVE INFORMATION.

NOTICE The information provided is preliminary, and subject to change without notice. Please check for the latest information when using this product in your design.

#### - YAMAHA CORPORATION

Address Inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Iwata,

Shizuoka, 438-0192, Japan Tel. +81-539-62-4918 Fax.+81-539-62-5054

1 dx. + 61-339-02-303

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8586, Japan Tel. +81-3-5488-5431 Fax.+81-3-5488-5088

■Osaka Office Universal City Wako Bldg.

6-2-82, Shimaya, Konohana-ku, Osaka, 554-0024, Japan

Tel. +81-6-6465-0325 Fax.+81-6-6465-0391