After visiting the Genos CPU complex yesterday, let’s take a look at the two Yamaha SWP70 tone generators in Genos.

The SWP70 is the latest generation, top-of-the-line Yamaha tone generator. We know that the SWP70 is capable of both sample-playback AWM2 synthesis and FM-X synthesis as demonstrated by the Yamaha Montage and MODX.

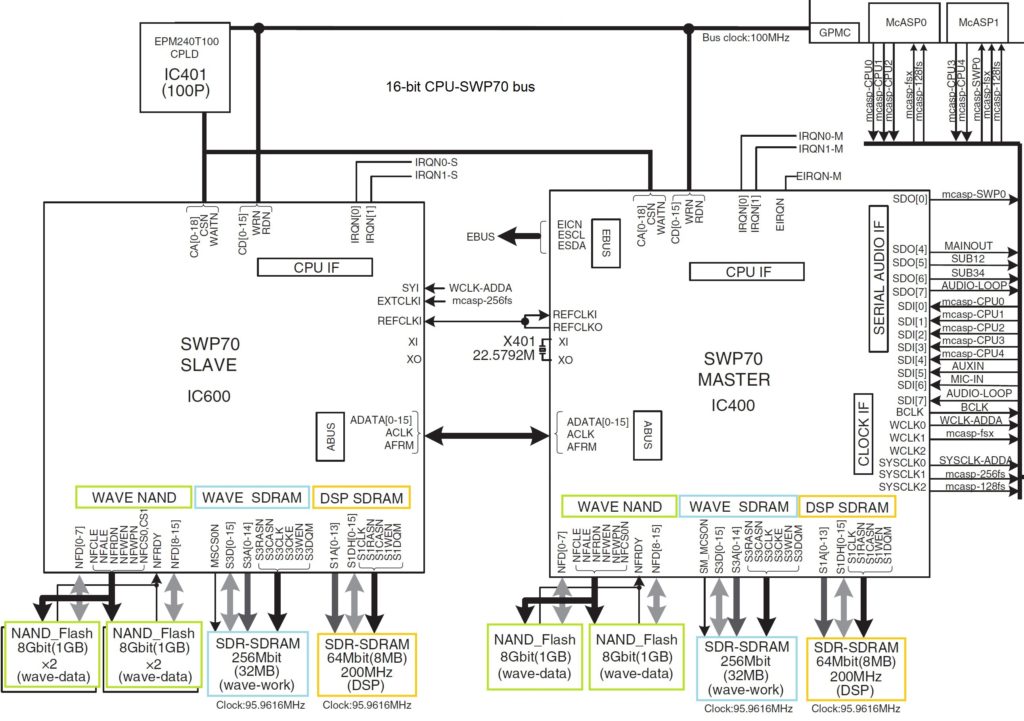

[Click image to enlarge.]

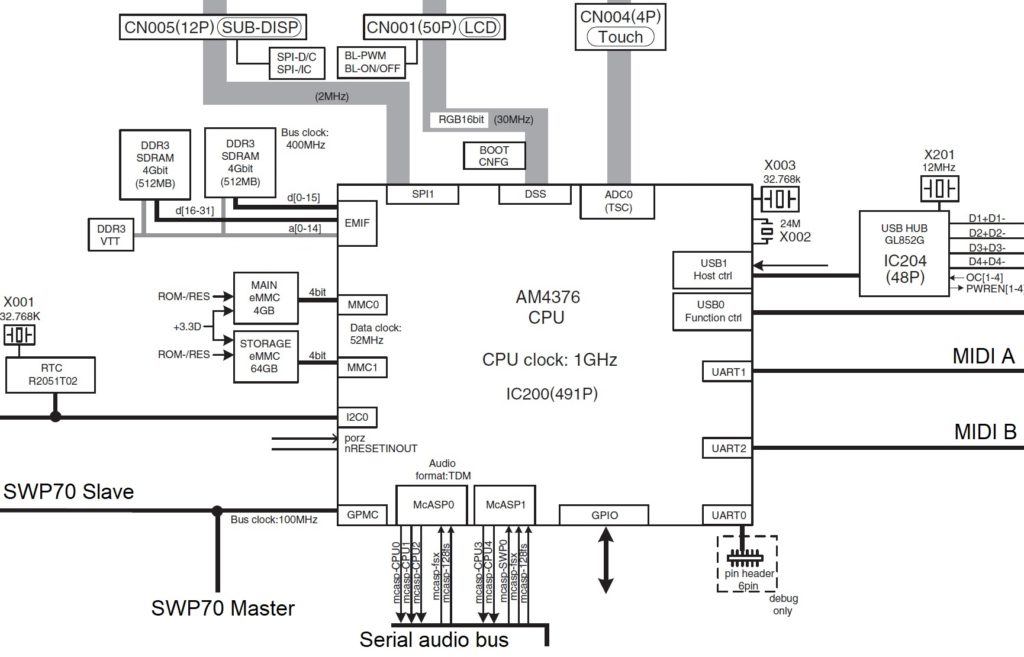

The two SWP70s are organized as a master and slave pair, each with different connections and dedicated memory units. The SWP70s communicate with the TI AM4376 processor over the CPU-SWP70 bus. The bus is arbitrated by a programmable logic device (CPLD). The data path is 16 bits and there are 19 address bits. Bus clock speed is 100MHz.

The main CPU sends control messages, etc. to the SWP70s through this bus. The main CPU also uses this bus to write waveforms (“samples”) in the SWP70 wave memory. Please note that the 100MHz bus isn’t fast enough to sustain so-called sample streaming from bulk storage. As mentioned in my previous article about the main CPU, the embedded bulk memory devices (eMMC) would not be able to supply samples fast enough for streaming either. Plus, write time to NAND flash is quite slow — another strike against streaming.

The Master SWP70 has extensive connections to the serial digital audio bus that interconnects the main CPU, tone generation, analog to digital converstion (ADC) and digital to analog conversion (DAC). Here’s a few notable connections:

- The main CPU sends five digital audio streams to the Master SWP70.

- The Master SWP70 sends one digital audio stream to the main CPU.

- The Master SWP70 sends the MAIN OUT, SUB 12 and SUB34 streams to their respective DACs.

- The Master SWP70 receives the AUX IN and MIC IN streams from their respective ADCs.

- The AUDIO-LOOP stream is a loop-back from the Master SWP70 to the Master SWP70.

Genos serial digital audio resources and capabilities are substantially less than Montage. In short, Montage has a Yamaha SSP2 processor dedicated to digital audio much like a Steinberg UR interface. This version of the Genos hardware will never have the extensive digital audio capabilities of Montage.

Another important interface is the Yamaha EBUS. Genos has an ARM M3 microcontrollers that scan the knobs, sliders, buttons and keys. The microcontroller sends these inputs on the EBUS. The EBUS is a slow-speed, serial I2C bus. User inputs are quickly encoded and are sent directly to tone generation. Nifty. The direct connection decreases latency by keeping the main CPU out of the message path. Montage and MODX have an EBUS, too. It’s an essential feature of Yamaha high-end design.

As Gandolf would say, “On to the Forest of Memories!”

Each SWP70 has two working memories:

- WAVE SDRAM (light blue)

- DSP SDRAM (orange)

Both working memories have dedicated address and data paths. The data paths are sixteen bits wide. The required memory capacity is too large to integrate on the SWP70 integrated circuit (IC), so separate commodity memory devices are used instead.

The DSP SDRAM is working memory for DSP computations. Certain kinds of effects are memory intensive — reverb and delay effects, in particular. The DSP SDRAM is a fast read/write working memory for effects processing.

The WAVE SDRAM is the working memory which holds the most recently streamed and used waveform samples. Random access to data in NAND flash is relatively slow. The WAVE SDRAM is a fast random access cache for samples in current use. The SWP70 behaves like the controller and cache within a commodity solid state drive. It streams waveform samples into cache as fast as possible via sequential reads to the WAVE NAND. The incoming samples are stored in the WAVE SDRAM and are played back from WAVE SDRAM.

Yamaha’s architecture is often (unfairly) slagged on two points:

- Why doesn’t Yamaha stream from a commodity SSD?

- Why doesn’t Yamaha use a commodity x86 motherboard for tone generation?

Yamaha combined the best parts of a commodity SSD and hardware tone generation in one component (the SWP70). This is a strategic low-latency advantage. The SSD SATA bus is quite unnecessary. The Yamaha architecture lowers power consumption, component count and most importantly, latency.

As to commodity motherboard, see Korg Kronos (big, heavy and hot).

WAVE NAND memory (light green) is implemented using commodity Open NAND Flash Interface (ONFI) devices. This is the same NAND flash employed in commodity, SATA-based SSDs. The Slave SWP70 has four gigabytes (4GBytes) of waveform memory while the Master SWP70 has two gigabytes (2GBytes). Storage is split into upper and lower bytes for a total data path width of 16 bits. The SWP70 accesses the upper and lower bytes in parallel. (Each ONFI channel is 8 bits wide.) Thus, Yamaha double the transfer bandwidth from NAND flash.

Presumably, the Slave WAVE NAND contains the Genos factory preset waveforms and the Master WAVE NAND contains user expansion waveforms. The Genos specifications split polyphony between preset and user voices. Expansion memory is limited to something just shy of 2GBytes. So, this inference is reasonable.

Now that you’ve read this far, you should have solid footing in Yamaha synth and arranger hardware architecture. Of course, there are many additional details about clock speeds, displays, touch panel, etc. However, you should have a better appreciation for and understanding of the basic data flows and storage units.

Copyright © 2019 Paul J. Drongowski

Source: Yamaha Genos Service Manual (Copyright Yamaha)

[Update: 18 October 2019]

Just a quick addendum about the SSP2 chip and the Steinberg URs. The SSP2 is built into the UR242, UR44, UR28M and UR824. Steinberg have a spiffy iOS app, dspMixFx, which exposes the SSP2’s functionality. Quoting Steinberg:

dspMixFx brings the flexibility and sound of Yamaha’s SSP2 DSP chip to your iOS device. Built in Steinberg’s UR824, UR28M, UR44 and UR242 interfaces, this custom-designed DSP chip runs the acclaimed REV-X reverb, Sweet Spot Morphing Channel Strip and Guitar Amp Classics effects. The free dspMixFx app allows you to control all DSP features and create your own latency-free mixes on your iPad and iPhone with effects, ideal for live recording sessions where getting exactly the right sound for performers is paramount. dspMixFx is also compatible with other iOS audio apps, offering full operation when using third-party apps with the DSP-powered interfaces in Steinberg’s UR range.

The REV-X reverb built into the UR824, UR28M, UR44 and UR242 is a complex reverb algorithm developed by Yamaha. Renowned for its high density, richly reverberant sound quality, with smooth attenuation, spread and depth that work together to enhance the original sound, the REV-X features three types of reverb effects: Hall, Room and Plate simulations with reverb time and level control.

Thanks to its SSP2 chip, the Montage provides conversion to and from a DAW roughly on par with a Steinberg UR interface.